Modulare Framework-Architektur

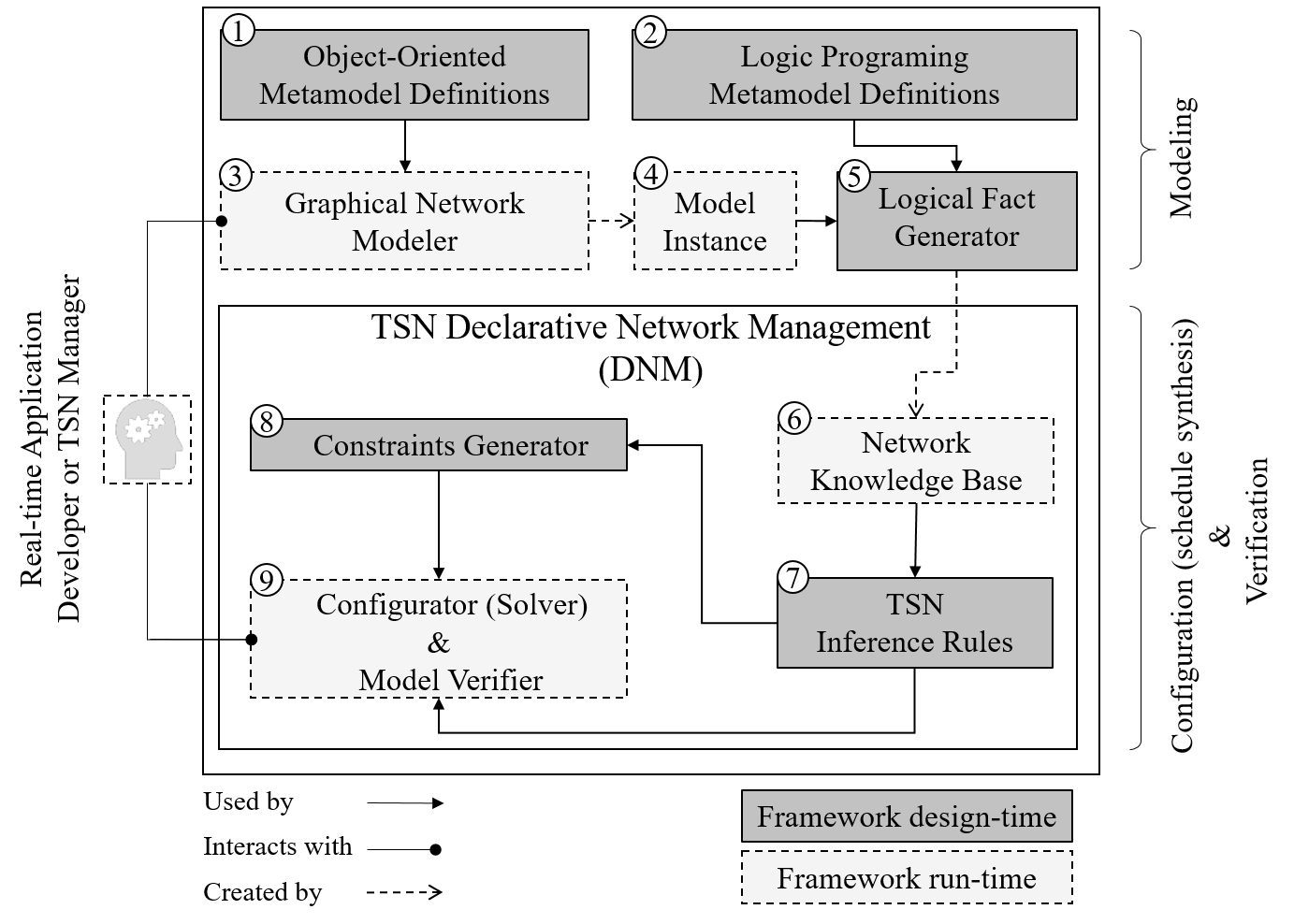

Um die TSN-Konfigurations- und Verifikationsprozesse zu automatisieren, bieten wir ein vielseitiges und modulares Framework. Wir vereinen die Stärken objektorientierter Modellierung und Logikprogrammierungskonzepte. Angemessene Schnittstellen werden implementiert, um die Systemkomplexität vor den Framework-Endbenutzern zu verbergen. Mit Fokus auf das IEEE 802.1Qbv Scheduling wird ein erstelltes grafisches Modell in Prolog in eine Netzwerk-Wissensdatenbank umgewandelt. Die Fakten und Inferenzregeln werden verwendet, um die erforderlichen Informationen zu extrahieren, um die Planungseinschränkungen aufzubauen und zu lösen. Mithilfe von Verifikationsabfragen in der Wissensdatenbank können gewünschte infrastrukturelle Eigenschaften verifiziert werden.

Generieren der Gate-Control-Listen

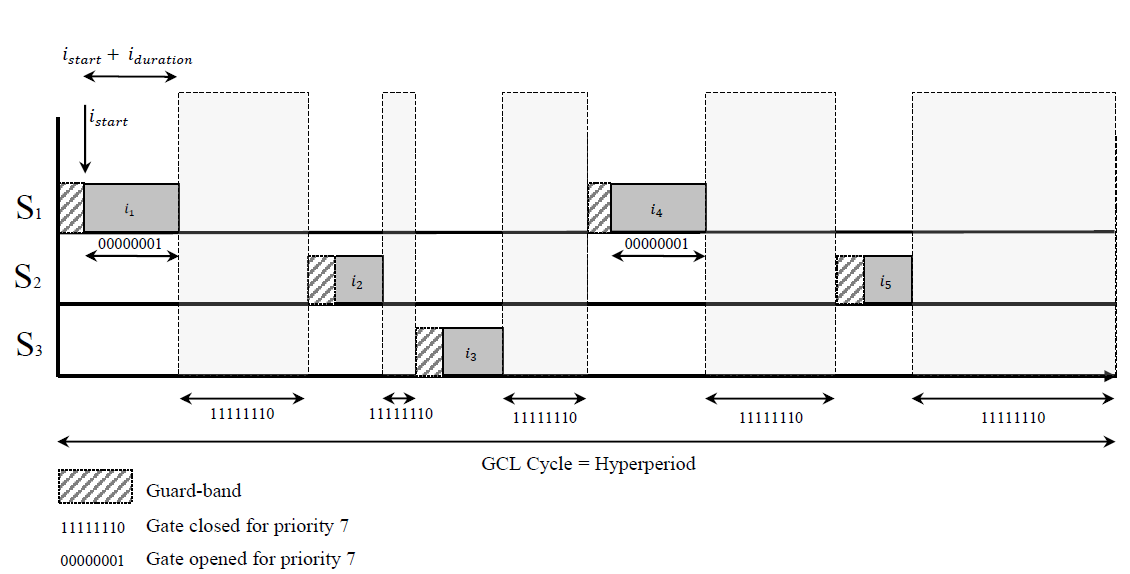

Das Endergebnis der Syntheseprozedur enthält die gültigen Offsetwerte für jeden zeitgetriggerten IEEE 802.1Qbv-Stream, wenn der Löser keine widersprüchlichen Beschränkungen findet oder die Synthese terminiert (NP-vollständiges Problem). Mit den Offsets der Streams eines realisierbaren Zeitplans generieren wir die GCL-Einträge und übertragen sie an die relevanten Netzwerkports.