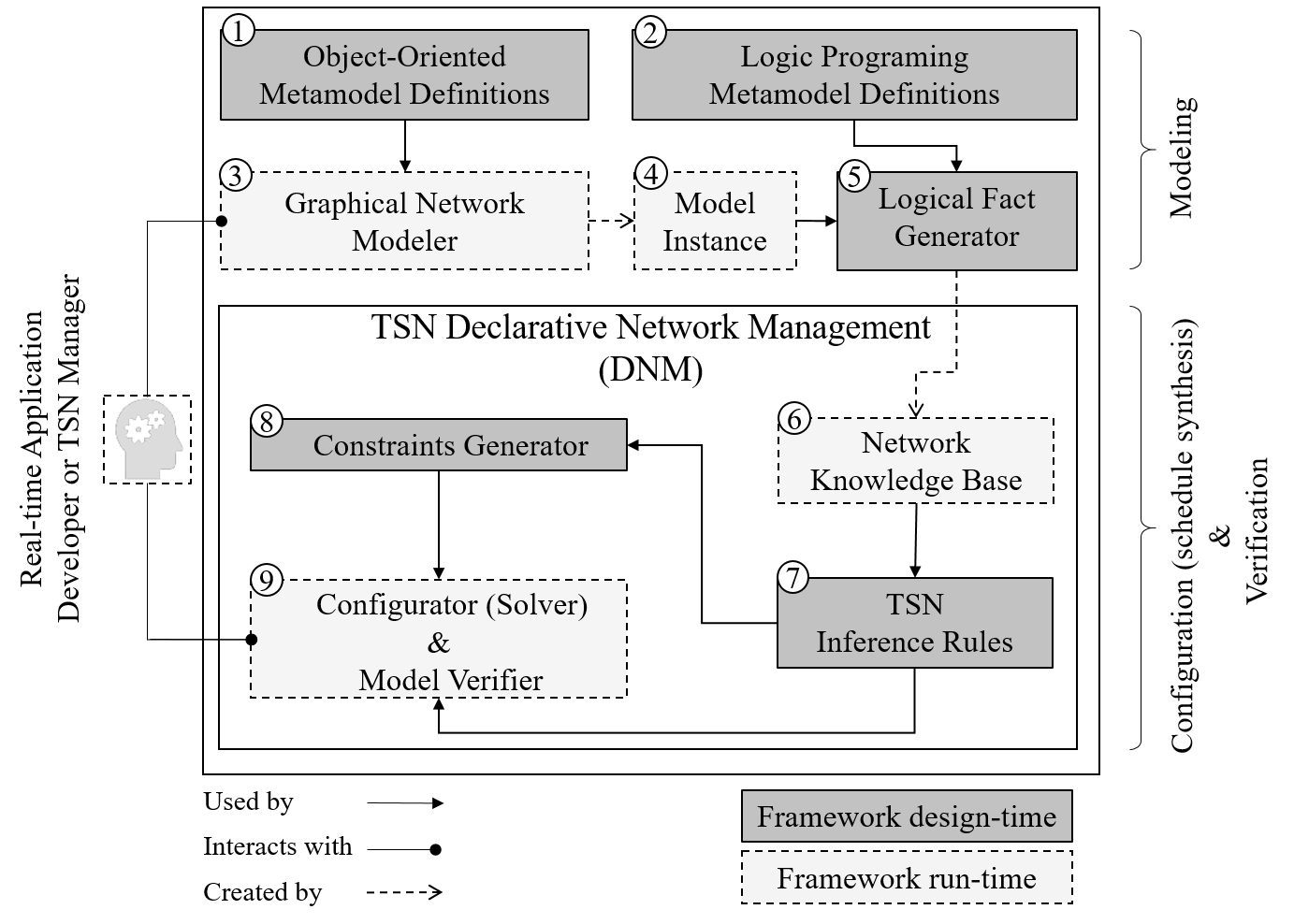

Modular Framework Architecture

To automate the TSN configuration and verification processes, we offer a versatile and modular framework. We combine the strengths of object-oriented modeling and logic programing concepts. Adequate interfaces are implemented to hide the system complexity from framework end-users. With a focus on the IEEE 802.1Qbv scheduling, a created graphical model is transformed into a network knowledge base in Prolog. The facts and inference rules are used to extract the required information to build and solve the scheduling constraints. Using verification queries on the knowledge base, desired infrastructural properties can be verified.

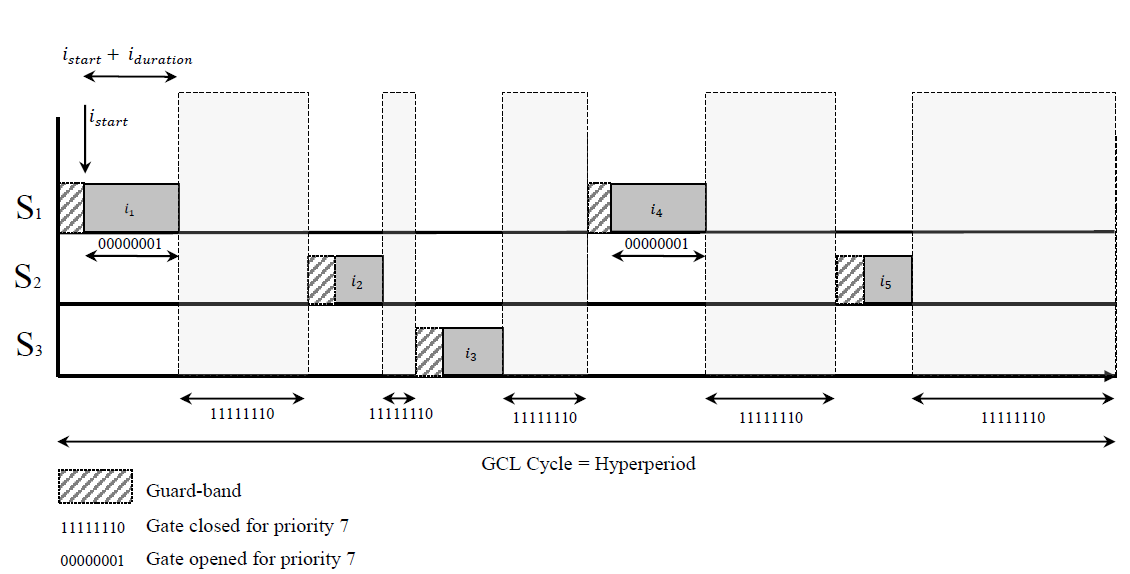

Generating the Gate Control Lists

The final result of the synthesis procedure contains the valid offset values for each time-triggered IEEE 802.1Qbv stream if the solver does not find any conflicting constraints or the synthesis terminates (NP-complete problem). Having the offsets of streams of a feasible schedule, we generate the GCL entries and transfer them to the relevant network ports.